Forum › Autour de l’Amiga › Amiga OS 4 – MorphOS – UAE – AROS › [UAE] WinUAE

- Ce sujet contient 293 réponses, 15 participants et a été mis à jour pour la dernière fois par

jouet24, le il y a 7 mois et 1 semaine.

jouet24, le il y a 7 mois et 1 semaine.

-

CréateurSujet

-

23 avril 2017 à 19 h 57 min #3138Staff

Aladin

Aladin

- Level 25

- Messages : 15381

WinUAE émulateur Amiga

Site officiel:

http://www.winuae.net/Traduction française:

http://www.tradu-france.com/

Pour ajouter le support des IPF, il faut ajouter les librairies CAPSImg.dll et/ou CAPSImg_x64.dll vers les exécutables winuae.exe et/ou winuae64.exe:

http://www.softpres.org/downloadDiscussion en anglais:

http://eab.abime.net/showthread.php?t=85939 -

CréateurSujet

-

AuteurRéponses

-

26 janvier 2022 à 20 h 57 min #135392Staff

Zarnal

Zarnal

- Level 22

- Messages : 7959

J’ai déjà une liste de ce qui ne va pas avec la 4.9.

Pas grand chose en fait.

Pas grand chose en fait.Quoi par exemple ?

Batman-Caped Crusader, Formula One, Phenomena-Dots. Au cycle. Soucis d’interruptions. Et ce dont on ne s’est pas encore aperçu.

Pour faire simple, il faudra attendre la 5.0 pour avoir le 100% de fidélité ( hors bugs potentiels d’émulation bien entendu ).

Avec la nouvelle émulation du Blitter, l’émulation des interruptions CPU ( IPL ) est devenue insuffisante ( alors qu’elle était Ok avant ).

Attention : il y a moyen de faire fonctionner ces titres. Mais pas au cycle.

A1200 Commodore mutant " FrankenAmiga" + 68040 + 8MO + SD 8go - A1200 ESCOM. HD 20MO. Mon meilleur et seul A500 : WinUae. CPC 6128-CPC 464.

29 janvier 2022 à 20 h 16 min #135595Staff Zarnal

Zarnal

- Level 22

- Messages : 7959

Un visuel sera plus parlant :

https://youtu.be/0kOuoifNhK4@Aladin la b8 est dispo depuis quelques minutes. :p

A1200 Commodore mutant " FrankenAmiga" + 68040 + 8MO + SD 8go - A1200 ESCOM. HD 20MO. Mon meilleur et seul A500 : WinUae. CPC 6128-CPC 464.

4 février 2022 à 14 h 47 min #136013Staff Aladin

Aladin

- Level 25

- Messages : 15381

WinUAE 4.9.1 beta 8 (29 Janvier 2022)

http://eab.abime.net/showthread.php?t=109203Changelog:

– Le calcul de la position finale du plan de bits de collision de sprite n’a pas été mis à jour vers l’émulation du chipset 4.9.0+. Il n’a probablement pas causé de problèmes car il était trop grand et il ne pouvait probablement pas causer de collisions parasites.

– Le correctif b6 ECS Denise CSYNC a interrompu la suppression verticale lorsque EXTBLANKEN=1. Fait seulement une différence visible si le mode était bizarre (pas le pilote de moniteur WB)

– Si le démarrage programmé du mode HSYNC est plus tard que la normale, utilisez-le à la place de la configuration standard de type VGA. (Position horizontale plus correcte si mode bizarre)

– Encore une autre mise à jour du comparateur Copper. WAIT et SKIP changent à nouveau, tous mes tests de fichier d’état fonctionnent toujours (et celui qui ne fonctionne pas aussi maintenant). La synchronisation de la vérification de la comparaison SKIP n’est pas la même que WAIT, SKIP semble vérifier le résultat de la comparaison juste avant le chargement de la prochaine instruction de cuivre (comparaison SKIP active tant que les bits IR1 et IR2 0 sont définis)

– correction de la mise à jour du numéro de bitplane b4, si le nombre de bitplane était augmenté après le début de hsync mais avant la fin de hsync, parfois le changement de nombre de plans de bits était ignoré jusqu’à la ligne suivante.

– Le mode de filtre « par défaut » s’ajuste désormais également automatiquement si la taille horizontale ne correspond pas à la verticale (par exemple, si l’horizontal est embauché mais que la verticale n’est pas doublée : doublez automatiquement la verticale en utilisant la mise à l’échelle du filtre). Les autres modes ne sont pas encore mis à jour car cela peut casser les configurations existantes.

– Mise à jour du nombre de cycles du mode « CE » 490b25 68030+ MMU annulée qui la rendait trop lente par rapport au mode non MMU correspondant.Téléchargement:

http://eab.abime.net/showpost.php?p=1529561&postcount=1464 février 2022 à 14 h 48 min #136014Staff Aladin

Aladin

- Level 25

- Messages : 15381

WinUAE 4.9.1 beta 9 (01 Février 2022)

http://eab.abime.net/showthread.php?t=109203Changelog:

– b8 La mise à jour du filtre « par défaut » n’était pas terminée. Maintenant, l’image est automatiquement mise à l’échelle en entier si l’image d’origine est la moitié (ou moins) de la taille de la fenêtre hôte/plein écran.

– Le changement de MMU b8 n’a pas beaucoup changé car MMU + CE n’est pas le « vrai » mode CE mais un MMU normal + quelques ajustements de synchronisation. (Parce qu’il n’y a pas grand intérêt). Ajustements de synchronisation ajustés, maintenant MMU + CE ne devrait pas être beaucoup plus lent que le mode CE non-MMU.

– Le filtre PAL (et probablement d’autres filtres logiciels qui utilisent YUV en interne) avait de mauvaises couleurs depuis la version 4.3.0, 32 bits uniquement.Téléchargement:

http://eab.abime.net/showpost.php?p=1530063&postcount=160

http://www.tradu-france.com/index.php?page=fullstory&id=8274 février 2022 à 14 h 51 min #136015Staff Aladin

Aladin

- Level 25

- Messages : 15381

WinUAE 4.9.1 (Février 2022)

https://www.winuae.net/Changelog:

4.9.0 bogues corrigés:

– Le JIT indirect était instable.

– JIT activé + émulé (pas uaegfx) La corruption de la carte RTG était possible dans certaines situations.

– Fuite directe du tampon de shader en mode 3D 11.

– Crash de démarrage de la carte de pont x86 AT (A2286 et A2386SX).

– Les modes de lores 15 et 16 bits de la carte PCem RTG ne doublaient pas correctement horizontalement.

– L’option Supprimer l’artefact entrelacé a ajouté 1 décalage de ligne de balayage aux plans de bits et aux sprites.

– Mises à jour et correctifs du chipset personnalisé et du mode d’affichage programmé.Bugs plus anciens corrigés:

– La souris commencerait à bouger de manière erratique si l’émulateur fonctionnait en continu depuis plus de 10 heures.

– La mise à l’échelle des entiers ne fonctionnait correctement que si les résolutions horizontales (lores, embauches, superhires) et verticales (non doublées, doublées) correspondaient. Les lores filtrés avaient de mauvaises couleurs si le mode graphique hôte était 16 bits.

– Mode NTSC et passage du logiciel en PAL : l’affichage n’était pas correctement étiré verticalement.

– Les filtres logiciels basés sur YUV avaient de mauvaises couleurs (32 bits uniquement)

– Paula a configuré le mode 4us (GCR) mais un disque MFM 2us normal dans le lecteur : les rapports d’index de disque n’étaient pas fiables.Mises à jour:

– Améliorations du mode d’affichage programmé (positionnement, suppression, etc.)

– La superposition uaegfx Picasso96 fonctionne désormais correctement avec le glissement d’écran.Nouvelles fonctionnalités:

– Il est désormais possible de taper (presque) normalement en mode warp. Les pressions sur les touches du clavier (si elles ne sont pas des touches qualificatives) sont immédiatement relâchées en mode Warp.

– L’émulation d’imprimante Epson n’imprime plus chaque page en tant que document séparé.

– Ajout du hack de désactivation de l’IDE scsi.device. Rend le démarrage nettement plus rapide sur OS39 et les versions KS plus récentes si l’IDE de la carte mère n’est pas nécessaire.

– Prise en charge planaire de l’émulation SVGA PCem Cirrus Logic activée. Picasso96 prend en charge le mode planaire 4 bits/16 couleurs.

– Le filtre « par défaut » et les filtres à échelle entière doublent désormais automatiquement horizontalement ou verticalement si les résolutions horizontale et verticale sont différentes (par exemple, lores + doublement vertical)Téléchargement:

https://www.winuae.net/

http://www.tradu-france.com/index.php?page=fullstory&id=8284 février 2022 à 15 h 32 min #136022 DocteurGeek

DocteurGeek

- Level 8

- Messages : 624

Merci

4 février 2022 à 16 h 42 min #136032Staff

4 février 2022 à 16 h 42 min #136032Staff Zarnal

Zarnal

- Level 22

- Messages : 7959

Il n’y a plus qu’à attendre la V 5.0 pour la finition.

Mais là, je pense qu’il va certainement prendre une petite pause bien méritée.

A1200 Commodore mutant " FrankenAmiga" + 68040 + 8MO + SD 8go - A1200 ESCOM. HD 20MO. Mon meilleur et seul A500 : WinUae. CPC 6128-CPC 464.

4 février 2022 à 19 h 41 min #136046 DocteurGeek

DocteurGeek

- Level 8

- Messages : 624

C’est clair qu’il n’a pas chômé. On a déjà de quoi bien s’amuser.

4 février 2022 à 20 h 04 min #136048 Mandrake

Mandrake

- Level 8

- Messages : 797

Super justement la souris étaraque je l’avais souvent sur winuae

Rien n'est jamais perdu, tant qu'il reste quelque chose à trouver. (pierre DAC)

Amiga 1200 3.2.1 + Amitek A1200 FPU 68882 8M + CF 32G

Amiga 1200 3.1 + MTECH 1230/28 8M + CF 32G

Juke-box Rock-ola Max 477 (capacité 80 single 45 tours) 1979

Revox B77 MKII 1975

Collection audio :

https://urlz.fr/j10t5 février 2022 à 1 h 12 min #136069 Klassik

Klassik

- Level 5

- Messages : 216

WinUAE est une merveille

5 février 2022 à 8 h 33 min #136082 Kimy

Kimy

- Level 17

- Messages : 3523

Tout à fait !! Qu’est-ce que l’on ne ferait pas sans lui.

C’est quand même dingue qu’il puisse y avoir autant de matériels supportés dessus.

2 octobre 2022 à 17 h 49 min #149874sink

- Level 6

- Messages : 362

une nouvelle version est sortie, la liste de correction est enorme! :)

3 octobre 2022 à 10 h 38 min #149898 DocteurGeek

DocteurGeek

- Level 8

- Messages : 624

une nouvelle version est sortie, la liste de correction est enorme! :)

Oui mais attention ce n’est pas une 4.9.2 finale c’est la bêta 1 elle amène beaucoup de bugs.

19 décembre 2022 à 21 h 22 min #153381Staff Aladin

Aladin

- Level 25

- Messages : 15381

WinUAE 4.9.2 beta 1 (01 Octobre 2022)

http://eab.abime.net/showthread.php?t=112041Changelog:

– Ajout du mode overscan « Ultra extreme debug ». La trame complète est entièrement visible, le blanking horizontal et vertical est désactivé (y compris le borderblank). Les changements de COLOR0 sont toujours visibles.

– L’allocation du cycle d’accès au bus du chipset du CPU n’était pas totalement précise. En fait, la partie du cycle consacrée à l’adressage et la partie du cycle consacrée au transfert de données étaient interverties. Ce problème existe depuis l’introduction du mode CE. Corrige par exemple Batman the Caped Crusader. (Une seule différence de cycle a suffi à le corriger..). Cela peut casser certains anciens fichiers d’état.

– L’émulation du 68000 STOP a été réécrite, l’utilisation des cycles et le timing de démarrage des interruptions sont maintenant entièrement précis.

– Si toutes les conditions de démarrage du plan de bits étaient actives à l’exception de la verticale DIWSTRT et que DIWSTRT était écrit plus tard avec une valeur verticale == verticale actuelle, le DMA du plan de bits démarrait immédiatement mais il devait y avoir un retard de 2 cycles. Si la DMA du plan de bits était désactivée mais que toutes les autres conditions étaient déjà actives et qu’ensuite DMACON était écrit pour activer la DMA du BPL : la DMA démarrait 1-2 cycles trop tard.

– Si le DMA bitplane (assez court) se termine avant que tous les slots sprites aient été traités, les slots sprites restants peuvent toujours fonctionner normalement (les sprites ne sont inhibés que lorsque le signal interne d’activité bitplane est actif). Cela peut également déclencher un bug très désagréable (inconnu jusqu’à présent ?) du chipset : lorsque la dernière récupération DMA du plan de bits a lieu, le DMA du sprite n’est plus inhibé par le DMA du plan de bits (une sorte de bug off-by-one) et si le même slot a un sprite actif, il entrera en conflit avec le DMA du plan de bits. Cela peut provoquer une écriture DMA inattendue dans un autre registre personnalisé (au lieu de BPLxDAT), la plage possible est de 0x100 à 0x11E. Par exemple, s’il s’agit de BPLCON0 (0x100), l’affichage peut être corrompu ou le moniteur peut perdre la synchronisation (ou afficher le message « No signal ») si le bit ERSY est activé. (Devinez comment ce bogue a été découvert…). C’était assez déroutant quand un programme de test très innocent provoquait soudainement une perte de synchronisation de l’affichage uniquement sur du matériel réel). Ceci est maintenant émulé avec précision et le débogueur DMA enregistrera les conflits.

– Les conflits de slot de rafraîchissement de plan de bits sont émulés avec précision (voir ci-dessous).

– Ajout de la configuration de la méthode de synchronisation du moniteur. La valeur par défaut est « Combiné » (correspond aux versions précédentes de l’UAE qui combinent les deux modes), C-Sync : utilise le signal de synchronisation composite comme source de synchronisation, HV-Sync : utilise des signaux de synchronisation horizontale et verticale séparés (VGA). Certains modes programmés peuvent présenter des différences entre les modes de synchronisation ou ne fonctionner qu’en mode de synchronisation HV ou en mode de synchronisation C dans le monde réel. Par exemple, ECS Denise ne peut pas générer simultanément une synchronisation C valide et un blanking horizontal programmé. AGA n’a pas cette limitation.

– L’écran émulé est maintenant effacé si les réglages du mode d’affichage programmé sont impossibles (l’écran réel perdrait la synchronisation, deviendrait effacé ou afficherait « aucun signal »), par exemple des impulsions de synchronisation vraiment trop courtes ou vraiment trop longues, BPLCON0 ERSY réglé sans genlock, BEAMCON0 BLANKEN ou CSYTRUE et le réglage du moniteur CSYNC sélectionnés, etc. Si un ancien fichier d’état est chargé avec ERSY réglé sans genlock : activez le genlock pour éviter un écran blanc inattendu.

– Un écran blanc de resynchronisation de l’affichage a été ajouté au panneau d’affichage. (Simule le délai de resynchronisation du mode d’affichage « moderne »). Si cette option n’est pas activée, le compteur FPS de l’OSD affichera temporairement « —« .

– Le débogueur DMA avait une adresse erronée affichée pour le deuxième cycle de cuivre WAIT/SKIP. (était identique au cycle de lecture précédent)

– Résolution Hires et bit BPLCON1 hires activé (ou shres et bit BPLCON1 shres) : un décalage horizontal d’un pixel peut être apparu sur le côté droit de l’écran. Mode AGA et non sous-pixel uniquement. (Skidmarks II en mode hires).

– Le RTC est automatiquement activé si le chipset extra=<modèle sans RTC> et que le système possède une RAM rapide, une RAM lente ou une extension de RAM par puce.

– Multiplicateurs d’horloge entiers 68000/010 plus élevés (4x+) en mode CE : le timing d’accès au chipset n’était pas précis.

– Emulation du bug de Denise A1000 : les sprites se terminent horizontalement 1 pixel plus tard que la fin de la fenêtre horizontale du bitplane. Actuellement activé lorsque A1000 Agnus est sélectionné.

– Remplacement du compteur interne de cycles 32 bits par un compteur 64 bits, ce qui simplifie la logique interne car la gestion ennuyeuse du retournement du compteur n’est plus nécessaire.

– La collision entre champs de jeu (collision complète) ne fonctionnait que si la même ligne avait au moins un sprite actif. (4.9.0).

– Les collisions entre sprites ne fonctionnaient pas correctement (4.9.0).

– Le blanking horizontal était absent si le mode écran programmé était actif sans blanking horizontal programmé (le blanking câblé aurait dû être actif).

– L’émulation de la CIA a été remaniée, avec une précision de cycle complète. Voir ci-dessous.

– Le nombre maximal de lignes verticales non entrelacées autorisé en mode programmé est désormais de 800 (au lieu de 592), les modes programmés spéciaux de 700+ lignes sont possibles et compatibles avec les vrais moniteurs SVGA.

– La restauration du fichier d’état ne restaurait pas correctement les valeurs statiques des BPLxDAT (affecte uniquement les programmes OCS/ECS qui utilisent le mode « 7-plane » et ne mettent à jour les BPLxDAT qu’au démarrage). (cassé dans la 4.1.0)

– Mise à jour des cas spéciaux de cycle zéro du cuivre, émulation de la différence de longueur de ligne impaire/paire. La liste du cuivre qui « déborde » au début de la trame suivante est émulée, si le cuivre a une demande DMA en attente lorsque le COPJMP se produit, le démarrage du COPJMP est retardé d’un cycle du cuivre. Auparavant, l’état du cuivre était réinitialisé au cycle 0 et le démarrage retardé était mis en file d’attente, ce qui n’est pas correct car les cycles 0 et 2 de la première ligne sont toujours normalement disponibles pour la liste de cuivre de la trame précédente.

– Le démarrage du blitter avait parfois un cycle de ralenti supplémentaire (4.9.0)

– Le mode ligne de Blitter avec largeur de blit != 2 est maintenant émulé avec précision et dessine correctement des « lignes » d’aspect étrange (auparavant, il ne faisait rien ou la ligne avait un aspect normal).

– L’interruption du blitter commençait 1 cycle trop tard. (+1 a été ajouté il y a longtemps parce qu’il corrige une démo, mais le bogue réel était la gestion du registre INTREQ).

– Si Paula active le bit INTREQ en interne (pas en écrivant dans INTREQ avec le CPU ou le Copper) : La ligne IPL change 1 CCK plus tôt, avant que la lecture d’INTREQR renvoie le nouveau bit activé.

– Démarrage de l’émulation ou chargement du fichier d’état avant le démarrage de l’émulation : les variables d’état vblank n’ont pas été initialisées correctement, le premier champ a activé le DMA du sprite trop tôt. (4.9.0 ou .1). Le démarrage du hardreset n’était pas exactement le même que le démarrage initial, le CPU démarrait quelques cycles plus tard en cas de hard reset.

– Les changements de résolution en milieu d’écran sont maintenant parfaits au pixel près (AGA complètement implémenté, OCS et ECS Denise seulement partiellement corrects).

– Sauvegarde des registres de contrôle du modèle RTC MSM6242B dans le fichier RTC s’ils sont modifiés. Auparavant, seuls les registres de contrôle du RF5C01A (et la NVRAM) étaient sauvegardés.

– Les interruptions du port série et SERDATR sont maintenant exactes au niveau du cycle. (Seulement si le cycle exact de la mémoire du CPU est activé)

– Les interruptions de transmission du port série et les bits liés à la transmission SERDATR sont maintenant émulés même si le port série = aucun.

– Le mode optionnel de bouclage du port série a été ajouté. TX->RX. RTS->CTS. DTR->DSR+CD. C’est aussi précis au niveau du cycle (pour tester le timing IPL du cputester sans matériel supplémentaire, il suffit d’avoir un fil de liaison entre TX et RX).

– La deuxième banque de ROM étendue de 1M est maintenant divisée intérieurement en deux banques de 512k. Le début et la taille des banques non alignés causaient des problèmes dans certaines configurations.

– Le déplacement d’écran en mode mixte uaegfx Picasso96 v3.0+ est activé par défaut. 4.9.1 paramètre de ligne de commande « -p96test 1 » requis.

– 4.9.1 Le glissement d’écran de uaegfx Picasso96 sans le paramètre de ligne de commande « »-p96test 1″ plantait l’Amiga émulé.

– Les nouvelles fonctionnalités de uaegfx Picasso96 sont maintenant optionnelles (toutes activées par défaut). Fichier de configuration uniquement.

– uaegfx toutes les fonctions de Picasso96 sont maintenant entièrement « accélérées matériellement » (utilise le code natif côté hôte), à l’exception du dessin de ligne. Auparavant, certaines fonctions ne supportaient que les opérations courantes de minterms/masques, les opérations non supportées étaient gérées par le logiciel Picasso96. Les minterms qui lisent et inversent la destination n’inversent plus les bits inutilisés/alpha si le mode en possède (15bit/32bit). Toujours utiliser le paramètre RGBFormat dans D7 si disponible, au lieu de la variable RGBFormat de RenderInfo.

– Les modes d’affichage programmés par le chipset utilisent (encore) le timing de suppression horizontale pour calculer le positionnement de l’affichage. Il a été confirmé qu’au moins certains moniteurs SVGA multisync du début/milieu des années 1990 (par exemple Microvitec 1438) utilisent également le timing de blanking pour calculer la taille et la position de l’affichage au lieu de se baser uniquement sur le timing hsync/vsync.

– Les cartes RTG émulées matériellement qui ont une sortie rouge et bleue physiquement permutée (Spectrum, Piccolo, Piccolo SD64) ont de mauvaises couleurs en mode 24/32 bits.

– Piccolo Z3 et Piccolo SD64 Z3 avaient une taille logique de carte autoconfigurée incorrecte (ce qui faisait planter le pilote).

– Si la VRAM de la carte RTG émulée matériellement se trouvait immédiatement (pas d’espace d’adressage) après une région RAM/ROM et que le JIT direct était activé : les 4096 premiers octets (taille de page du CPU hôte) de la VRAM n’étaient pas entièrement compatibles avec le JIT direct et toute lecture ou écriture directe des 4096 premiers octets n’accédait pas correctement à la VRAM, ce qui provoquait des problèmes graphiques inattendus.

– Gestionnaire d’exception JIT direct simplifié, la structure de contexte d’exception win32 peut être utilisée pour lire et modifier directement n’importe quel registre du CPU hôte, il n’y a pas besoin de trampolines et de code auto-modifiant.

– L’émulation du modèle initial de mise sous tension de la Chip RAM et de la Slow RAM est activée par défaut (case à cocher dans le chipset avancé). Cela correspond maintenant à mon matériel réel (A500 OCS/A500 ECS/A1200) mais les configurations modifiées comme ECS Agnus dans la carte mère rev5 (ou plus ancienne) ne créent pas de modèles corrects. Les bits aléatoires ne sont pas générés, mais seulement un motif répétitif de tous les uns et de tous les zéros. Le modèle dépend du type de puce de la RAM et du fabricant. D’autres puces peuvent avoir des motifs différents.

– La lecture des données du disque retournait des données aléatoires même si aucun lecteur n’était sélectionné (devrait retourner uniquement des zéros). Corrige la corruption de l’écran original de Nitro Psygnosis. Corrige également un autre bogue connexe lorsqu’aucun lecteur n’est sélectionné et que la synchronisation du disque correspond à un effet secondaire qui provoquait le blocage de Juke Box 2 / Dreamdealers au démarrage.

– Passage à Visual Studio 2022.

– Taille de l’interface graphique par défaut plus grande et police légèrement plus grande si le bureau de Windows est suffisamment grand (au moins 1600*1024).

– Enfin, suppression d’un grand nombre d’avertissements de compilation (à l’exception de PCem).

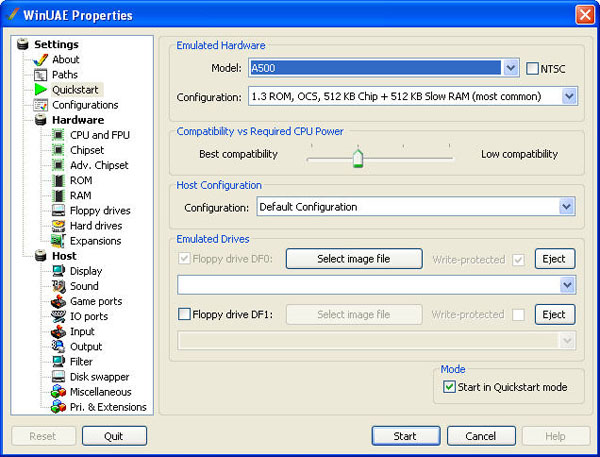

– L’élément initial de l’interface utilisateur du panneau Quickstart est maintenant DF0 : bouton de sélection d’image. Trop de changements accidentels de modèles Amiga..

– Suppression du support DirectDraw, ajout du support GDI (API win32 basic GDI). Différences de fonctionnement : le plein écran exclusif n’est pas supporté (passe en D3D11/9 si on essaie), tous les modes de mise à l’échelle de base et le curseur matériel uaegfx sont supportés.

– La colonne de pixels la plus à droite et la rangée de pixels la plus basse de la fenêtre Box Art n’étaient pas visibles.

– Le bouton de fermeture de la boîte de dialogue Crash dump ne faisait généralement rien.

– La boîte de dialogue du scanner de ROM n’utilisait pas la taille et les polices correctes de l’interface graphique.

– Mise à jour CyberStorm MK I : L’accélérateur et le SCSI ont été séparés. Le module CyberSCSI est maintenant une carte d’extension et possède une image ROM séparée (fonctionne de manière similaire au kit SCSI de Blizzard). La ROM principale ne doit être configurée que si le CPU est un 68060 car elle se plantera si le CPU est un 68040, elle est seulement nécessaire pour désactiver le FPU 68060. Le CSMK1 réel avait des ROMs vides si le CPU installé était un 68040.

– Le débogueur visuel DMA montre les cycles conflictuels sous forme de pixels rouges clignotants.

– Le débogueur DMA (à la fois en console et visuel) supporte mieux les variables/le basculement du nombre de lignes horizontales et verticales.

– Il n’était plus possible d’entrer dans le débogueur si le CPU était bloqué en état d’arrêt après être entré et sorti du débogueur une fois.

– Ajout des opérateurs OR, AND et XOR à la calculatrice du débogueur (|, &, ^).

– La commande v du débogueur ne plante plus si hpos ou vpos est hors de portée.

– La commande Debugger v montre maintenant (au moins temporairement) les valeurs d’adressage de ligne et de colonne (RAS et CAS) de la RAM de Chip. Très important pour le comportement des conflits REFPTR et refresh/bitplane.

– La commande sp du débogueur analysait les sprites attachés de manière incorrecte (depuis le début).

– Modification du commutateur CTRL+F12 plein écran/fenêtre : Si l’on est déjà passé du plein écran à la fenêtre. Le prochain CTRL+F12 reviendra en pleine fenêtre, et non en plein écran.

– La vérification du bloc de démarrage des disquettes du panneau de démarrage rapide utilisait la piste actuelle du lecteur (et non la piste 0). Cassé lorsque le support FloppyBridge a été ajouté.

– Réinitialisation de l’état de FloppyBridge lors du changement de type de lecteur de disquettes de/vers le type de lecteur FB vers un autre type de lecteur. Corrige la configuration uae à la volée lors du changement de type de lecteur de disquettes vers/depuis FB.

– Le point d’arrêt de Memwatch qui traversait une « banque » de 64k ne correspondait pas à la dernière « banque » de 64k si elle n’était que partiellement nécessaire.

– La fonction de débogage du code auto-modifiant (smc) efface maintenant les modifications détectées si le cache d’instructions du 68020+ est vidé.

– N’ajoute pas les entrées de l’historique des instructions du CPU lorsque celui-ci est arrêté.

– La position horizontale et verticale est maintenant incluse dans la sortie de l’historique du débogueur (H/HH).

– Ajout d’informations sur l’état d’arrêt du CPU au débogueur DMA (| = cycle d’arrêt, + = cycle d’arrêt et IPL supérieur détecté = arrêt se terminant bientôt).

– La valeur décimale du compteur de cycle horizontal du débogueur DMA a été supprimée et remplacée par l’état actuel de la ligne IPL (niveau d’interruption).

– Le débogueur DMA montre les opcodes du CPU dans leur forme basique (« NOP », « MOVE » etc), verticalement. Cela semble un peu bizarre mais je n’avais pas de meilleures idées…

– Le chipset avancé CD32 NVRAM ou C2P sans CD32 n’était pas entièrement supporté.

– Le mode Quickstart CD32/CDTV « se souvient » du réglage précédent de DF0 : et ne le désactive pas par défaut (même si le panneau Quickstart le montre comme désactivé).

– Le panneau Quickstart CD32/CDTV DF0 : ne pouvait pas être sélectionné/activé.

– uaegfx : mise à l’échelle automatique des nombres entiers supportée (choisit le multiplicateur d’échelle maximum entièrement visible), multiplicateurs horizontaux/verticaux manuels du panneau de filtre supportés.

– Le changement de moniteur END+F9 n’est plus câblé et peut être changé en utilisant le panneau d’entrée. (END+F9 debug colors when in lagless vsync mode is still hardwired)

– L’audio CD est maintenant toujours mélangé avec l’audio Paula. La prise en charge d’une sortie audio CD séparée a été supprimée.

– L’audio CD n’était pas repris si WinUAE n’était pas minimisé et si minimiser était configuré pour mettre l’émulation en pause.

– La configuration de la RAM Z2 n’était pas fiable. (4.9.0)

– Certains jeux laser américains n’avaient pas de support de désembrouillage de ROM. Ajout de variantes de ROM manquantes.

– Ajout du support Quickstart pour les American Laser Games.

– Si la configuration matérielle de l’arcade basée sur la ROM Quickstart (Arcadia ou ALG) est sélectionnée, le nom du fichier NVRAM est automatiquement réglé sur le nom de la ROM. Le chemin du fichier vidéo Genlock est également défini si la ROM ALG est sélectionnée. Les fichiers de configuration ne sont pas affectés.

– Ajouté toutes les ROMs KS officielles 3.1.4+ au scanner de ROM.

– Le tri de la liste des fichiers ROM a été modifié, ajout de groupements, tri par priorité de groupe d’abord (ROMs KS, ROMs KS étendues, ROMs de congélation etc…), puis par ordre alphabétique.

– La mise à l’échelle des nombres entiers avait des artefacts de mise à l’échelle qui dépendaient de la taille de la fenêtre et d’autres variables. (Ancien bogue)

– Ajout du chemin de la NVRAM dans le panneau Chemins. (Les fichiers NVRAM des matériels Arcade/CD32/CDTV se trouvent par défaut dans ce chemin).

– Parfois les anciens graphiques étaient temporairement visibles dans les modes RTG si le RTG avait des bordures noires visibles (dépend du mode de mise à l’échelle) et que l’écran était changé et que le nouvel écran avait une taille/résolution plus grande.

– CTRL+C dans la fenêtre de console ne ferme plus WinUAE. (CTRL+C dans les versions plus récentes de Windows peut fonctionner comme une opération de copie).

– Ajout d’un événement d’entrée de sélection de fichier d’enregistrement vidéo. Ceci démarre également l’enregistrement si le fichier a été sélectionné.

– La valeur du compteur FPS de la bordure de la fenêtre a un « R » ajouté si l’enregistrement est actif.

– La création d’un lien logiciel vers un système de fichiers de répertoire ne fonctionnait pas (renvoyait « objet non trouvé ») en mode de chemin relatif (Windows a besoin d’un chemin absolu lors de la création de fichiers de raccourci).

– Les liens souples de système de fichiers de répertoire ne sont résolus que si le répertoire contenant le lien est listé en premier ou si le lien souple est créé dans la même session (le lien souple est « mis en cache » par l’émulation du système de fichiers).

– Ajout de l’indicateur « Slow » au panneau RAM. S’il est activé, la banque de mémoire sélectionnée a un timing de Chip RAM mais n’est pas capable de Chip RAM. Le panneau avancé du chipset « C00000 is Fast RAM » a été supprimé, il n’est plus nécessaire. (N’affecte la vitesse du CPU que dans les modes de cycle exact).

– Les fonctions ECS Denise Genlock peuvent être activées manuellement : genlock_effects= ou p. « brdntran » peut être utilisé pour forcer l’activation du bit BPLCON2 BRDNTRAN, « brdrblnk » pour forcer l’activation du bit BPLCON2 BRDRBLNK. Séparés par une virgule. (par exemple « genlock_effects=3,15,p7 »)

– Correction d’un bug de sélection de la couleur des sprites de Genlock.

– Correction de l’émulation Genlock ECS Denise BPLCON2 BRDNTRAN. Pas vraiment testé par HW mais je pense que c’est censé donner un aspect normal à la bordure même si la couleur 0 est transparente pour la genlock.

– Emulation du bit Genlock ZCLKEN BPLCON3, s’il est activé, la broche de sortie vidéo de transparence genlock (PIXELSW) commence à sortir une horloge pixel de 14MHz. L’émulation crée une transparence alternée de la taille des pixels si elle est activée et si le genlock est configuré. (Ce qui est probablement ce qui se passe dans le monde réel aussi lorsque le genlock est connecté. A l’origine, il était probablement supposé être un signal de synchronisation des pixels pour les périphériques vidéo externes).

– Ajout d’un support optionnel pour les captures d’écran en png indexé avec une palette de 256 couleurs dans le panneau de sortie. Si la capture d’écran a plus de 256 couleurs uniques, le png 24-bit est créé comme précédemment. Il essaie également de garder l’ordre de la palette originale : d’abord les couleurs uniques de la capture d’écran sont collectées, puis les valeurs du registre des couleurs personnalisées sont collectées (valeurs à la fin du champ précédent), les couleurs de la capture d’écran sont comparées aux couleurs personnalisées, si la correspondance est trouvée, la couleur est marquée comme allouée. Ensuite, toutes les couleurs restantes (changements de couleur du cuivre, EHB, HAM, leds à l’écran, noir de masquage etc…) sont ajoutées à la palette. Si le total est supérieur à 256, un png 24 bits est créé. Le mode 256 couleurs essaie également de préserver les 32 premières entrées de la palette de couleurs. (Préservé = la couleur n’est pas écrasée par une autre couleur même si la couleur n’est pas utilisée dans la capture d’écran).

– Support optionnel de la capture d’écran IFF (-screenshotiff ou screenshot_mode=2 registry/ini). Le mode IFF ne tente pas de préserver les 32 premières entrées de la palette de couleurs afin de conserver une profondeur d’image aussi faible que possible. IFF n’est pas (encore) compressé.

– Amélioration du support des citations ‘s’ et ‘W’ du débugueur, par exemple « W xxx « ab’c » fonctionne comme prévu.

– Réécriture majeure, suppression des doublons de code.

– Précision du cycle (les timers étaient précis au niveau du cycle auparavant mais pas beaucoup plus), bogues/ »fonctionnalités » de la CIA émulés. La plupart d’entre elles ont été héritées de la 6526.

– Le comptage de l’horloge électronique de la CIA et la synchronisation entre le CPU et l’horloge électronique ont été réécrits.

– Le calcul de la position horizontale de l’incrément du TOD CIA-B était défectueux, le TOD CIA-B était incrémenté trop tôt horizontalement et pouvait augmenter le TOD deux fois si le TOD était aussi modifié dans la même ligne ou l’incrément du TOD de la ligne pouvait être complètement manqué. Plus compatible/CE uniquement.

– L’incrémentation interne du TOD de la CIA par 1 est bizarre, la valeur incrémentée du TOD ne peut être mise à jour que toutes les 4 horloges E (je suppose que la mise à jour du timer complet est répartie en interne sur 4 cycles). Cela affecte également la synchronisation des interruptions d’alarme.

– La position de l’incrément TOD du CIA-A est maintenant précise au niveau du cycle, y compris le comportement ci-dessus toutes les 4 horloges E.

– La synchronisation de l’horloge électronique de l’accès au processeur de la CIA a été mise à jour pour inclure le retard causé par les signaux VPA/VMA.

– Les interruptions de la CIA sont retardées de 1 E-clock.

– De nombreux cas spéciaux non documentés ont été émulés, par exemple les valeurs 0 et 1 du timer latch fonctionnent de manière inattendue (pas très surprenant, la valeur zéro du timer n’a probablement pas été conçue pour être utilisée…).

– Si le timer CIA a été démarré en écrivant à TxHI (mode ONESHOT) avec le timer précédemment chargé avec la valeur==0 : l’interruption est générée 1 cycle plus tôt que normalement.

– Le minuteur B de la CIA qui compte le minuteur A déborde : Le temporisateur B décompte 2 cycles après que A ait débordé. C’était immédiat auparavant.

– Ajout de la phase de l’horloge électronique (0 à 4) dans le fichier de configuration. La phase de l’horloge E du vrai 68000 par rapport à l’horloge du CPU est aléatoire, décidée lorsque le système est mis sous tension. En tout cas, mon vrai A500 s’allume rarement dans l’état E-clock phase=0 (que l’UAE utilise par défaut). Habituellement, elle semble être à 2 ou 3. La phase peut être détectée par le logiciel en utilisant quelques astuces mais aucun programme normal ne s’en soucie.

– Le mot lu dans l’espace CIA-B renvoie maintenant le contenu correct du registre dans l’octet supérieur. Auparavant, il retournait le contenu du registre OU avec les données du bus précédent.

– Les accès CIA ont été ajoutés au débogueur DMA (nouvelle ligne).

– Les valeurs de la minuterie de vidage du registre CIA du débogueur n’étaient pas nécessairement des valeurs actuelles réelles mais des valeurs lors du dernier accès à un registre CIA.

– Option de cycle d’horloge électronique de la CIA ajoutée, A500 (68000 génère le timing de l’horloge électronique) a un timing d’horloge électronique légèrement différent de celui de A600 (Gayle génère l’horloge électronique). Option ajoutée au chipset Advanced. Aucun programme normal ne s’en soucie mais cette différence peut être détectée par le logiciel. La principale différence est que l’horloge électronique générée par Gayle est plus longue de 2 horloges CPU que l’horloge électronique interne du 68000, ce qui rend impossible les accès dos à dos à la CIA si l’Amiga est basé sur Gayle.

– La plupart des cas spéciaux ne sont émulés que si le CPU est plus compatible et pas le plus rapide possible.Téléchargement:

http://eab.abime.net/showpost.php?p=1567624&postcount=1

https://www.tradu-france.com/index.php?page=fullstory&id=85519 décembre 2022 à 21 h 22 min #153382Staff Aladin

Aladin

- Level 25

- Messages : 15381

WinUAE 4.9.2 beta 2 (08 Octobre 2022)

http://eab.abime.net/showthread.php?t=112041Changelog:

– Le blanking de resynchronisation de l’écran était bloqué (~1s d’écran vide lors du changement de mode).

– Le transfert de données des périphériques en série émulés en internes (par exemple le lecteur de laserdisc) était instable.

– Les données de la taille de l’autoconfig de la carte RTG émulée par le matériel Z3 ont été corrigées puis à nouveau cassées.

– Certains contrôleurs SCSI NCR710+ se bloquaient.

– Les bits d’état du port série n’étaient pas corrects dans tous les modes du CPU.

– Refonte de la table d’émulation des instructions internes du CPU, utilisation d’une table séparée pour les instructions qui renvoient le nombre total de cycles et les instructions qui comptent les cycles de manière interne (modes cycle-exact).

– La boîte de dialogue du type de disquette du panneau de démarrage rapide était partiellement coupée si l’interface graphique utilisait une taille par défaut plus petite.

– L’installation complète de D3D9 était accidentellement requise (message d’erreur d3dcompiler_47.dll).

– Le retour automatique au mode GDI (si D3D11 et D3D9 ne sont pas disponibles) était toujours tenté.Téléchargement:

http://eab.abime.net/showpost.php?p=1568553&postcount=39

https://www.tradu-france.com/index.php?page=fullstory&id=856 -

AuteurRéponses

- Vous devez être connecté pour répondre à ce sujet.